After all, NVIDIA RTX 4070 SUPER has more L2 cache

In its official announcement presentation, the company made a mistake.

RTX 4070 SUPER now has 48MB of L2 cache available instead of 36MB. NVIDIA had an error in the official specifications shared as part of its official launch presentation. This error has just been fixed.

At CES 2024, four new cards were announced for desktop PC gamers. AMD introduced the Radeon RX 7600 XT GPU in the mid-range segment at $329, while NVIDIA is focusing on models that are at least twice as expensive, launching the RTX 4070 SUPER at $599. This model replaces his existing RTX 4070 card and is currently discounted to $549.

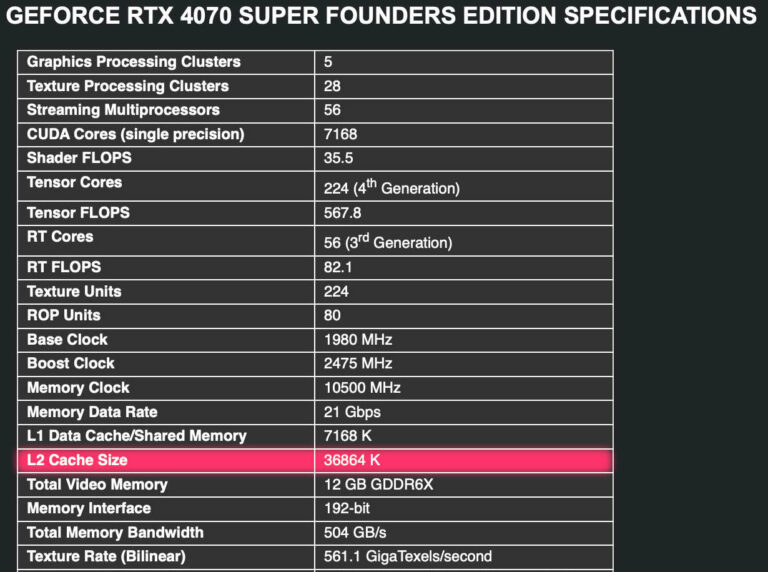

The official specs listed in the review guide list the RTX 4070 SUPER model’s L2 cache size as 36 MB. This information was also included in the official marketing slides. However, NVIDIA has updated the specs to confirm that this model does indeed use 48MB of L2 cache. No other changes were reported.

NVIDIA RTX 4070 SUPER specs, source: NVIDIA

L2 cache size plays an important role in the Ada Lovelace GPU architecture memory subsystem. This factor can limit VRAM pool queries and is especially important for cards with limited 128-bit memory buses in the RTX 4060 series. For the RTX 40 Series, NVIDIA has updated the size of L2 cache on all consumer GPUs, offering up to 96 MB of L2 cache on AD102 and up to 32 MB on AD107/106.

The AD104, on which the RTX 4070 series is based, has a total of 48 MB of L2 cache. The RTX 4070 SUPER uses the AD104 GPU with more SMs enabled (56 out of 60), so it makes no sense for NVIDIA to limit it to 36 MB. This was also the spec for his original RTX 4070.

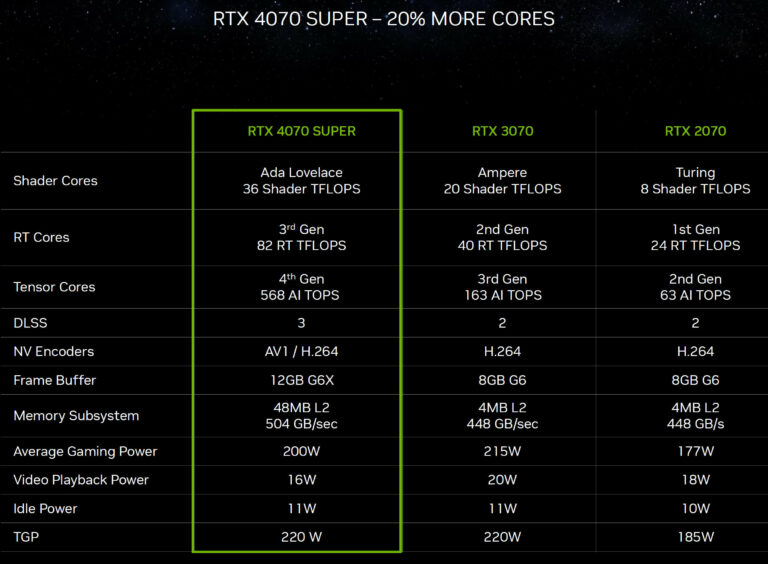

With that in mind, the RTX 4070 SUPER with 20% more core count and 33% more L2 cache will definitely show a measurable improvement in gaming. However, the reference spec model may be limited by its default TDP of 220W, which is only 20W more than the RTX 4070.

The RTX 4070 SUPER is scheduled to launch on January 17th, with early reviews arriving a day early.

| NVIDIA GeForce RTX 40 | ||||

|---|---|---|---|---|

| VideoCardz.com | SMS | CUDA core | memory bus width | L2 cache |

| AD102 | ||||

| AD103 | ||||

| AD104 | ||||

| AD106 | ||||

| AD107 | ||||